01∏¥µ©¥Û—ßÕ≈∂”»∆π˝EUV𧓒

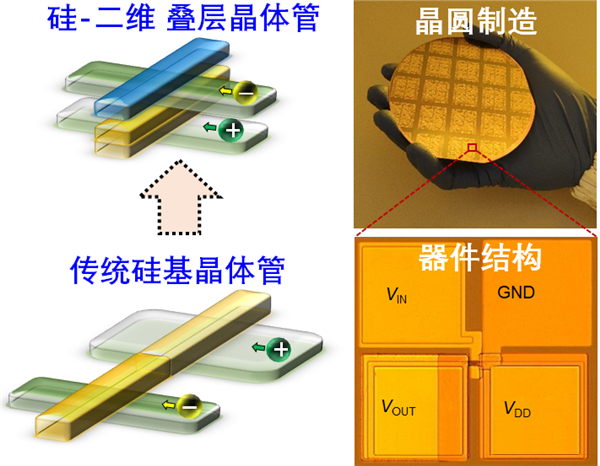

≤˙∆∑£∫ø·Ó£ i5 12490F Intel CPUŒ“√«÷™µ¿£¨Ã·∏þ∞εºÃ–‘ƒÐæÕ“™‘ˆº”æßÃÂπеƒ ˝¡ø£¨»Áπ˚µ•Œª√ʪ˝µƒæß∆¨“™»ðƒ…∏¸∂ýµƒæßÃÂπУ¨æÕ–Ë“™Õ®π˝Àı–°µ•‘™æßÃÂπеƒ≥þ¥Á¿¥ µœ÷£¨¿˝»Á7nmΩ⁄µ„“‘œ¬“µΩÁ π”√º´◊œÕ‚π‚øúº ı µœ÷∏þæ´∂»≥þ¥ÁŒ¢Àı°£”…”⁄º´◊œÕ‚π‚øÅ˱∏∏¥‘”«“∂‘Œ“π˙–Œ≥…¡À∏þ∂»µƒºº ı¬¢∂œ”Î∑‚À¯£¨‘⁄œ÷”–ºº ıΩ⁄µ„œ¬ƒÐπª¥Û∑˘Ã·…˝ºØ≥…√Ð∂»µƒ»˝Œ¨µ˛≤„ª•≤πæßÃÂπÐ(CFET) ºº ı∂‘Œ“π˙÷ÿ“™“‚“ÂÕπœ‘°£

”…”⁄»´π˪˘CFETµƒπ§“’∏¥‘”∂»∏þ«“–‘ƒÐ‘⁄∏¥‘”𧓒ª∑æ≥œ¬ÕÀªØ—œ÷ÿ£¨∏¥µ©¥Û—ߌ¢µÁ◊”—ß‘∫µƒ÷Ð≈ÙΩà ⁄£¨∞¸Œƒ÷–—–æø‘±º∞–≈œ¢ø∆—ß”Îπ§≥×ߑ∫µƒÕÚæ∞—–æø‘±£¨¥¥–¬µÿ÷≥ˆ¡Àπ˪˘∂˛Œ¨“Ï÷ ºØ≥…µ˛≤„æßÃÂπкº ı°£∏√ºº ı¿˚”√≥… ϵƒ∫Û∂Àπ§“’Ω´–¬–Õ∂˛Œ¨≤ƒ¡œºØ≥…‘⁄π˪˘–æ∆¨…œ£¨≤¢¿˚”√¡Ω’þ∏þ∂»∆•≈‰µƒŒÔ¿ÌÃÿ–‘£¨≥…π¶ µœ÷4”¢¥Á¥Ûπʃ£»˝Œ¨“Ï÷ ºØ≥…ª•≤π≥°–ß”¶æßÃÂπУ¨‘⁄œýÕ¨µƒπ§“’Ω⁄µ„œ¬Ω´ºØ≥…µÁ¬∑µƒºØ≥…√Ð∂»∑≠±∂£¨≤¢ªÒµ√¡À”≈‘Ωµƒ∆˜º˛–‘ƒÐ°£

œýπÿ≥…π˚“‘°∂πË∫Õ∂˛¡ÚªØÓ‚“Ï÷ ª•≤π≥°–ß”¶æßÃÂπа∑£®Heterogeneous Complementary Field-effect Transistors Based on Silicon and Molybdenum Disulfide£©Œ™Ã‚”⁄±±æ© ±º‰2022ƒÍ12‘¬08»’∑¢±Ì”⁄π˙º ∂•º‚∆⁄øØ°∂◊‘»ªµÁ◊”—ß°∑£®Nature Electronics£©°£

∏¥µ©¥Û—ß—–æøÕ≈∂”Ω´–¬–Õ∂˛Œ¨‘≠◊”æßÓ˝»Î¥´Õ≥µƒπ˪˘–æ∆¨÷∆‘Ï¡˜≥㨠µœ÷¡Àæß‘≤º∂“Ï÷ CFETºº ı°£œý±»”⁄πË≤ƒ¡œ£¨∂˛Œ¨‘≠◊”æßõƒ‘≠◊”≤„æ´∂» π∆‰‘⁄–°≥þ¥Á∆˜º˛÷–æþ”–”≈‘Ωµƒ∂Ãπµµ¿øÿ÷∆ƒÐ¡¶°£¿˚”√π˪˘ºØ≥…µÁ¬∑µƒ±Í◊º∫Û∂À𧓒£¨Ω´∂˛¡ÚªØÓ‚(MoS2)»˝Œ¨∂—µ˛‘⁄¥´Õ≥µƒπ˪˘–æ∆¨…œ£¨–Œ≥…p–ÕπË-n–Õ∂˛¡ÚªØÓ‚µƒ“Ï÷ CFETΩ·ππ°£

∂˛¡ÚªØÓ‚µƒµÕŒ¬π§“’”屫∞π˪˘ºØ≥…µÁ¬∑µƒ∫Û∂À𧓒¡˜≥Ã∏þ∂»ºÊ»ð£¨¥Û∑˘ΩµµÕ¡À𧓒ƒ—∂»«“±Ð√‚¡À∆˜º˛µƒÕÀªØ°£¥ÀÕ‚£¨¡Ω’þµƒ‘ÿ¡˜◊”«®“∆¬ Ω”Ω¸£¨∆˜º˛–‘ƒÐ∏þ∂»∆•≈‰£¨ π“Ï÷ CFETµƒ–‘ƒÐ”≈”⁄¥´Õ≥π˪˘º∞∆‰À˚≤ƒ¡œ°£∆‰∑¥œý∆˜‘ˆ“Ê‘⁄3Vπ©µÁ ±∏þ¥Ô142.3 V/V £¨‘⁄≥¨µÕ—ππ©µÁ0.1V ±∆‰‘ˆ“Ê¥Ô1.2 V/V«“π¶∫ƒµÕ÷¡64pW°£

∏√ºº ıŒ¥¿¥Ω´Ω¯“ª≤Ω÷…˝–æ∆¨µƒºØ≥…√Ð∂»£¨¬˙◊„∏þ√Ð∂»¥¶¿Ì∆˜£¨¥Ê¥¢∆˜º∞»Àπ§÷«ƒÐµ»”¶”√µƒ∑¢’π–Ë«Û£¨≤¢÷˙¡¶Œ“π˙¥Ú∆∆π˙Õ‚‘⁄¥Ûπʃ£ºØ≥…µÁ¬∑¡Ï”Úµƒºº ı∑‚À¯°£