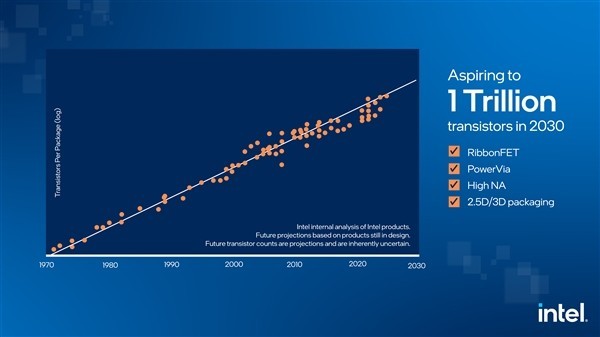

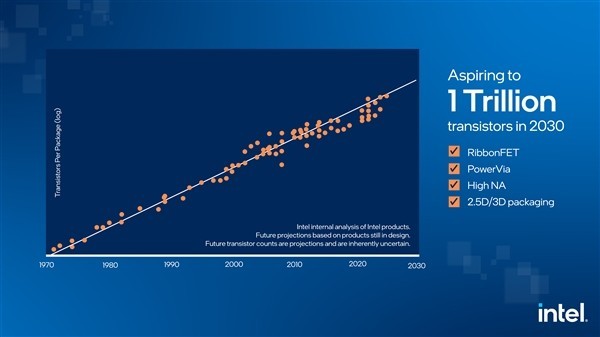

��IEDM 2022 IEEE���ʵ������������ϣ�Intel�����˶����µļ���ͻ�ƣ��������᳹�Ѿ�����75���Ħ�����ɣ�Ŀ������2030��������оƬ����1���ڸ����������Ŀǰ��10�������������/�ܶ�һֱ�Ǻ����뵼�弼����������Ҫָ�꣬Ŀǰ�Ѿ�����������оƬ1000���ڸ�����ܣ�����Intel Ponte Vecchio GPU��

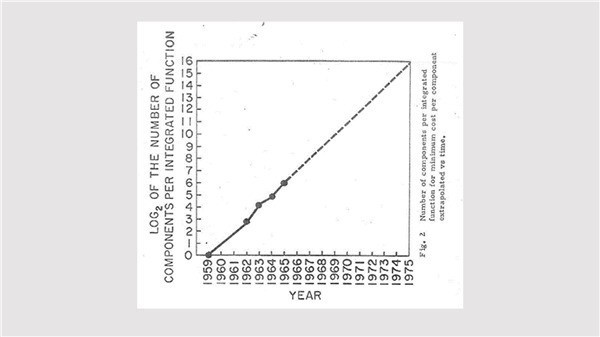

Ħ������ԭ��

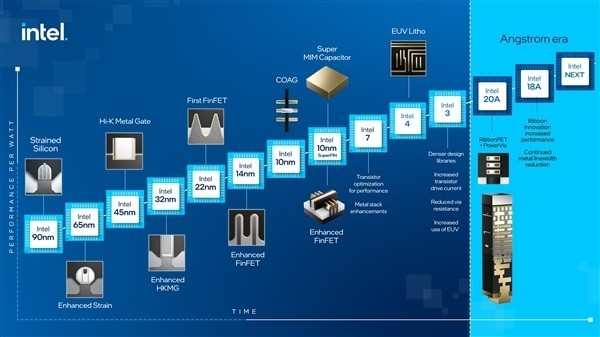

��Ӧ��衢��K����դ����FinFET���徧��ܣ���δ����RibbonFET GAA����դ������ܡ�PowerVia���ù��磬�ٵ�2.5D EMIB��3D Foveros��Foveros Direct/Omni��װ������Intelһֱ�ڴӸ�������ƶ�Ħ�����ɡ�

IEDM 2022�����ϣ�Intel��¶����������ļ���ͻ�ƣ�

1����һ��3D��װ��оƬ

���ڻ�ϼ���(hybrid bonding)���������ܶȺ�����������10����ͬʱ�����С��3�ף�ʹ�ö�оƬ�����ܶȺʹ����������ĵ�оƬSoC��

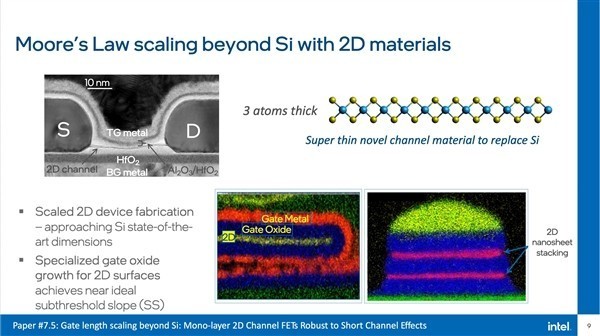

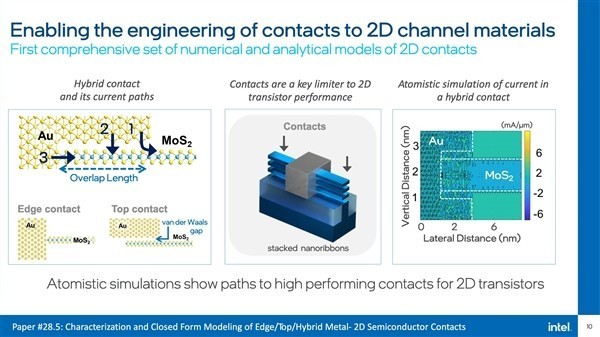

2������2D�����ڵ�оƬ�ڼ��ɸ��ྦྷ���

ʹ�ú�Ƚ���3��ԭ�ӵ�2Dͨ�����ϣ�Intelչʾ��GAA��ջ����Ƭ����˫դ���ṹ�ϣ������»�������©�����£�����˷dz�����ľ���ܿ����ٶȡ�Intel��һ�������ʾ��2D���ϵĵ�Ӵ����ˣ���ʵ�ָ������ܡ����е��Եľ����ͨ����

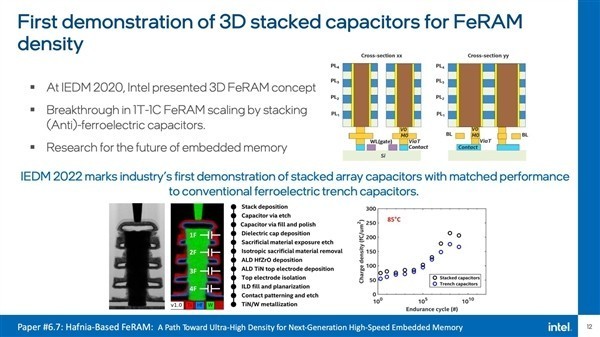

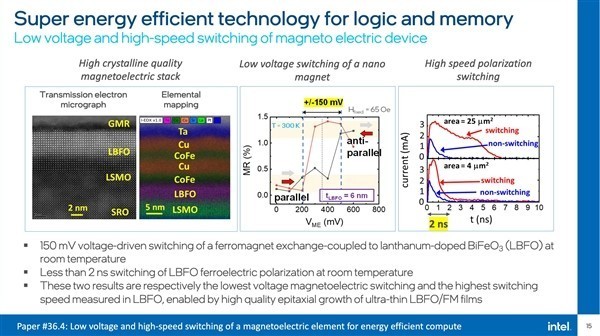

3�������ܼ�����Ч���ڴ���ͻ��

Intel�з��˿ɴ�ֱ�ѵ��ھ����֮�ϵ�ȫ���ڴ棬���״�չʾ��ȫ�µĶѵ�������ݣ�����������ͳ���繵�����ݣ�����������оƬ�ϴ���FeRAM��

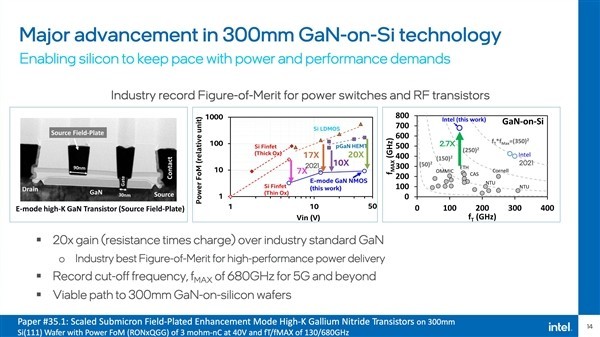

����Intel���ڴ���300����ֱ���Ĺ��ϵ����ؾ�Բ���ȱ��ĵ���������20����ͬ�£�Intel�ڳ�����Ч����Ҳȡ�����µ�ͻ�ƣ������Ǿ�����ڶϵ��Ҳ�ܱ������ݣ������ϰ��Ѿ�ͻ���������ܿ���ܴ���������¿ɿ����С�

Intel���칤��·��ͼ

Intel��װ����·��ͼ

��������ԭ�����£�����ת�أ���ע����Դ��Intel������ͻ�ƣ�3��ԭ�Ӻ�Ȳ��ϼ���1���ھ����https://diy.zol.com.cn/808/8083857.html