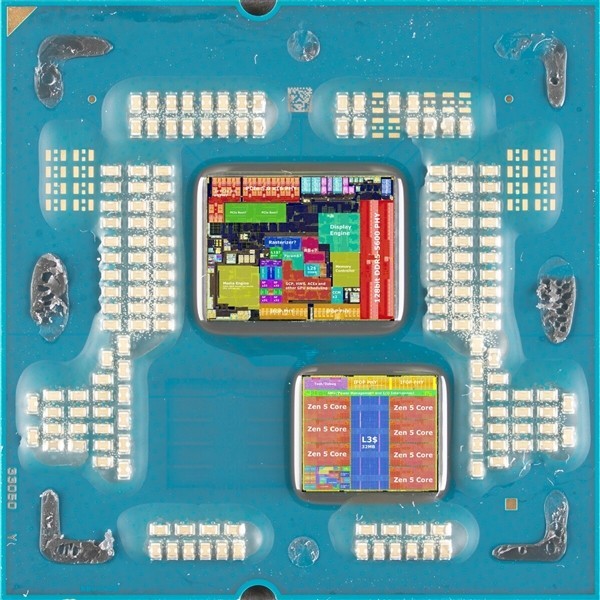

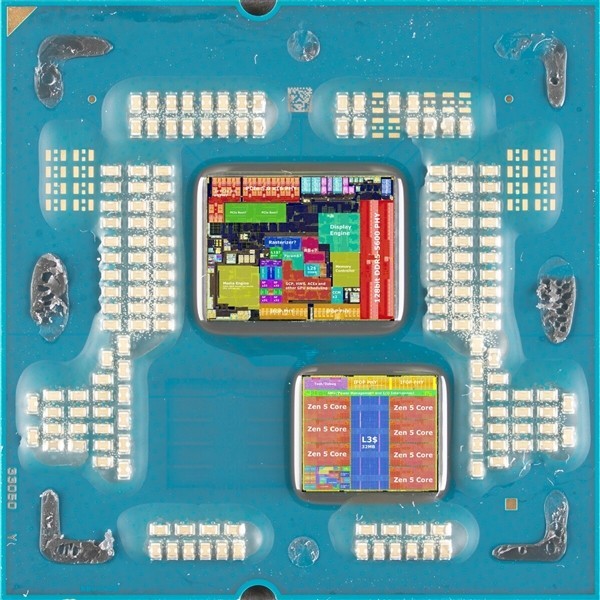

近日国外一些大神多位大神对锐龙9000系列进行了详细的拆解,让我们得以看到Zen5架构的详细信息,下面是锐龙9000系列的拆解。

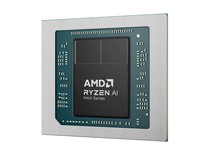

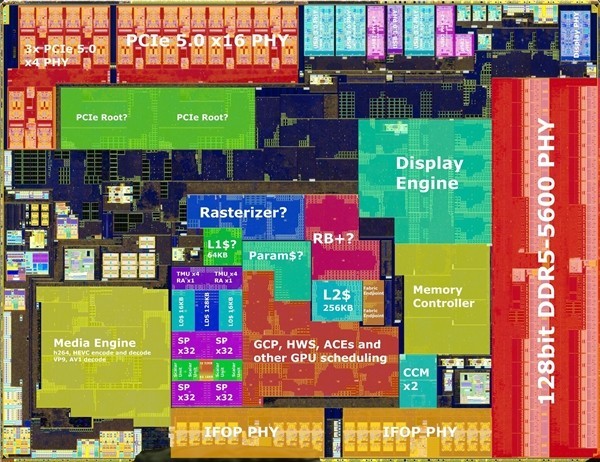

锐龙9000系列采用了经典的chiplet布局,两颗锐龙都是双CCD设计,锐龙7和锐龙5则是单CCD,并包含一颗IOD。其中CCD为N4P 4nm工艺,IOD则是N6 6nm工艺。

布局方面,锐龙9000系列依旧是共享缓存设计,所有核心共享的32MB三级缓存。在架构图的左下角,有一块紫色标记的区域,这个部分是专门用于测试和调试的。

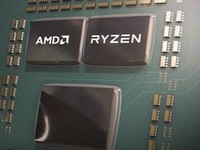

可以看到左侧占据了较大面积的部分是矢量执行单元,这部分主要用于执行浮点运算,并且支持完整的512位浮点路径,兼容AVX-512指令集。由于浮点运算通常会产生较多热量,因此该单元被设计在核心及整个CCD(Core Complex Die)的边缘位置,以便于更好地散热。

转向右侧,我们会发现这里是二级缓存的位置,它紧密连接着三级缓存,以加速数据访问速度。

而位于中心的部分则包含了处理器前端的核心组件,如指令预取与解码逻辑、分支预测机制、微操作缓存和调度器等。此外,这里还集成了32KB的一级指令缓存、48KB的一级数据缓存、整数执行单元以及负责内存读写的载入/存储单元。这一系列组件共同构成了处理器处理指令流的关键路径,对提升整体性能至关重要。

本文属于原创文章,如若转载,请注明来源:国外大神拆解锐龙9000系列 Zen5架构细节露出https://diy.zol.com.cn/905/9058398.html