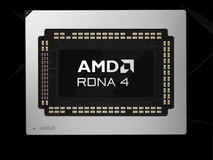

4月15日,AMD宣布其下一代代号为“Venice”(威尼斯)的霄龙处理器已率先采用台积电2纳米制程技术(N2)进行流片并投入生产。这款基于Zen 6架构的高性能计算(HPC)芯片预计将在明年正式推出。

同时,AMD还透露,其第五代霄龙处理器已经在台积电位于美国亚利桑那州的Fab 21晶圆厂完成投产与验证。根据该晶圆厂的技术水平推测,这很可能是指基于4纳米工艺的“Zen 5”标准核心版本。

AMD董事会主席兼首席执行官苏姿丰表示,台积电多年来一直是AMD的重要合作伙伴,双方研发与制造团队的深度协作推动了AMD持续推出领先行业的产品,并不断突破高性能计算领域的性能极限。此次成为台积电N2工艺及亚利桑那晶圆厂的主要高性能计算客户,正是双方紧密合作、共同创新的典范,展现了如何通过先进技术驱动未来计算的发展。

台积电董事长兼总裁魏哲家也对此表示,AMD作为台积电2纳米工艺技术以及亚利桑那晶圆厂的核心高性能计算客户,彰显了双方在技术升级方面的高度协同。通过合作,双方正在不断提升高性能芯片的性能、能效以及产量,为下一代计算技术奠定基础。魏哲家还表达了对未来进一步深化合作的期待,希望共同引领计算技术的未来发展。

本文属于原创文章,如若转载,请注明来源:AMD下一代霄龙处理器采用台积电2纳米制程技术生产https://diy.zol.com.cn/974/9742255.html