随着9月的来临,科技届年度春晚——苹果秋季发布会也将如约而至。不同于前几年,苹果在新品保密工作上的严丝合缝,这几年随着苹果全球布局产业链,产品保密的难度和可操作性近乎失衡,几乎每年的苹果新品都会被提前曝光,而今年更是如此。

可即便如此,全球科技用户,依旧对苹果新品的到来,充满期待。今年号称“十三香”的iPhone系列更是早早的,从内部架构到外观结构的全面曝光。其中,代表苹果手机核心竞争力的A15仿生芯片,无疑是业界最为关注的焦点。

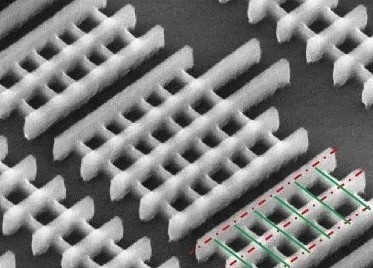

A15仿生芯片概念图

据供应链消息,iPhone13(命名待定)系列内置的全新A15仿生芯片,采用台积电最新5nm+工艺制程(N5P),是台积电目前量产最先进的制程工艺,苹果也是首个该工艺下的重磅客户,和去年iPhone12一致,苹果为此提前预备了超过1亿的5nm+工艺订单量,用来全面生产新iPhone所需要的A15仿生芯片。

那么问题来了,台积电5nm+工艺制程到底有何过人之处?芯片制造中,工艺制程又是什么?今天,我们就从新iPhone的5nm+工艺制程出发,聊一聊半导体的工艺制程。

01 工艺制程是什么?

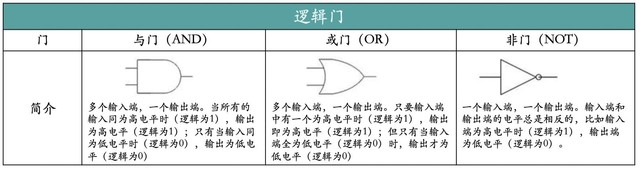

在了解工艺制程之前,我们需要明白芯片的工作原理,即利用半导体PN结的单向导电性原理,并利用多个晶体管串联的“与”、“或”、“非”构成逻辑门,将电信号转化为0、1数字信号,实现信号传递,从而最终实现单个电流开关驱动数以亿计晶体管进行工作,输出0和1数字信号,转化成二进制进行计算、存储。

在这里,受制于篇幅,就不再展开关于半导体PN结的论述,只需要知道它是由单质硅提炼而来,并具有单向的导电特性即可。

主要聊下能够实现逻辑门开关和闭合的晶体管,了解计算机的朋友对于这个名词应该不会陌生,也大都听过这个故事,全球第一台计算机ENIAC,是由超过17468个电子管、6万个电阻器、1万个电容器和6千个开关组成,每秒仅能运行5千次加法运算;

可其后随着晶体管的问世,IBM公司推出IBM7090型全晶体管大型机,计算性能得到了飞跃,运算速度达到每秒229000次,由此可见晶体管对于现代半导体生态的重要性。

晶体管经过多年工艺演变,已然从初代需要玻璃外壳保护的稀罕物,成为现代半导体工艺最为常见和最不可或缺的关键器件。

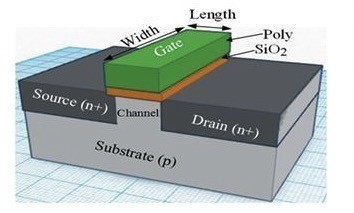

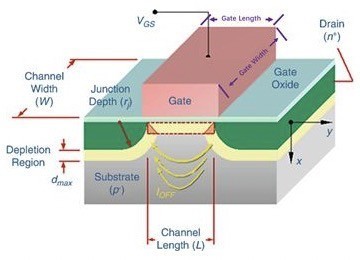

晶体管的内部结构,主要是由源极、漏极和位于它们之间的栅极所组成,其中的栅极长度,便是我们常常所言的工艺尺寸,或者说工艺制程,所谓28nm、10nm乃至于7nm,都是描述从源极到漏极之间栅极长度,业界称之为Gate Length。

02 工艺制程演变方向

根据芯片工作原理,我们其实能够知晓,芯片响应速度快慢,取决于单个晶体管内部两级之间的电荷流动速度,为了加速流动,一方面我们能够增加更多的晶体管数量,让电荷快速在不同晶体管中流转起来,另一方面更需要在单个晶体管内部不断缩短阻碍在两级之间的栅极长度,也就Gate Length。

以上两个方向,也就构成了当今世界各大半导体大厂各大工艺制程的主要延展方向,即不断提升芯片内部的晶体管数量,也就是单位空间内的密度问题,同时更要不断缩短单位晶体管内部的Gate Length,加速电荷流动。

当然值得注意的是,“工艺制程=栅极长度”,工艺制程等同于物理尺寸的说法,实际上从350nm之后,已然失效。那是源于,随着工艺制程推进,Gate Length物理尺寸的缩小已然没有规律可言,但部分业界从业者(没错就是三星、台积电)为了延续此前每隔一代大约能缩小0.7的规律,把后续的工艺制程,全都按照0.7的倍数进行缩小后命名。

举个例子28nm工艺制程后一代制程,即28*0.7约等于22,于是下一代工艺制程便被命名为22nm,接下来的14nm,乃至于10nm,7nm都是按照这个规律命名。

03 晶体管密度才是关键

那么既然后续命名和Gate Length物理尺寸没有任何联系,业界又是如何判定不同厂商之间的工艺带差呢?

那便是芯片内部的晶体管密度,通过对比芯片内部的晶体管密度多少,即可判定是否属于先进工艺或是同一工艺。

在这里,我们可以例举Intel 10nm工艺制程,根据公开消息,Intel 10nm工艺制程虽然在命名上不如台积电7nm工艺、三星7nm工艺制程响亮,可在晶体管密度方面,Intel 10nm远超台积电7nm工艺(DUV)和三星7nm(DUV),仅次于用EUV光刻机研发的台积电7nm+工艺。

由此可以看出,Intel 10nm和同期台积电、三星等厂商工艺制程属于同一水平,只是在命名上的不激进,导致被很多用户笑谈“挤牙膏”。

04 关于台积电N5+工艺

了解了工艺制程,回过头,再来看看台积电这次为新iPhone准备5nm+,到底又是何方神圣。

实际上,相较于火热的iPhone参数,关于台积电5nm+制程工艺消息,透露的并不多,我们可以试图从台积电5nm工艺一窥究竟。

此前,台积电总裁魏哲家就在技术论坛上表示,相较上一代7nm,5nm制程速度提升近15%,功耗则降低了30%,晶体管密度提升80%,妥妥的是新一代工艺制程,而该工艺也被首先运用在iPhone12之上,根据官方数据,采用台积电N5工艺的A14仿生芯片,内置118亿个晶体管,晶体管多了近30多亿,而CPU性能提升40%,而GPU则提升了近50%。

至于5nm+制程工艺,根据消息人士推测,将在5nm工艺的基础上,带来5%的额外速度提升和10%的功率提升。

至于具体提升,让我们拭目以待吧。

聊到这里,关于半导体工艺制程龙虎斗的上半部分就告一段落了。下一部分,我们将详细聊聊主要半导体大厂,现阶段的工艺制程,以及未来最具潜质的工艺制程演变FinFet工艺的周边。

本文属于原创文章,如若转载,请注明来源:从5nm+制程聊起 半导体工艺制程龙虎斗(上)https://diy.zol.com.cn/775/7753874.html